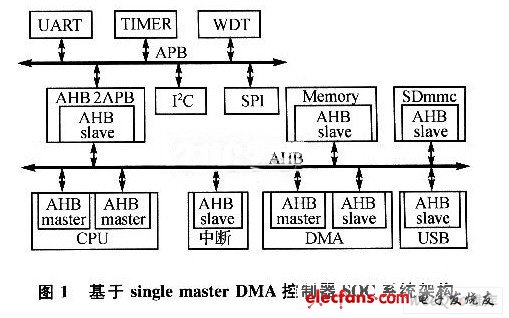

introduction With the rapid development of microelectronics technology, the scale of integrated circuits is rapidly increasing according to Moore's Law, and System ON Chip (SoC) technology has become the development trend of ultra-large scale integrated circuits. The continuous improvement of the performance of the SoC chip and the data exchange between the modules become the bottleneck for improving the operating speed of the microprocessor system. DMA (Direct Memory Access) is a mechanism for quickly transferring data. The DMA controller can effectively replace the load/store instructions of the microprocessor, significantly improving the parallelism of the system. DMA is the direct transfer of data between memory and input/output devices. It is a way to completely perform input/output operations by hardware. Data transfer can range from peripherals to memory, from memory to peripherals. However, the introduction of the DMA controller has also introduced factors that affect the system's response speed. This paper describes the architecture of the SoC system based on the DMA controller containing a single AHB master interface, analyzes the shortcomings, and introduces a SoC system architecture based on the new DMA controller to solve the proposed problem. 1 response speed to asynchronous events System real-time performance means that tasks can be completed within a limited time and respond to external asynchronous events in a timely manner. The time limit varies depending on the requirements of the application. The real-time performance of real-time systems is related to the hardware and software platforms used. The interrupt service response time of an embedded system refers to the period of time during which an interrupt service request is issued from an interrupt source, the interrupt service request is responded to by the processor, and the interrupt service routine of the interrupt source is started. The process scheduling in the embedded operating system is realized by interrupts. The response speed of the processor to asynchronous events occurring in the system or outside the system is a key factor determining the response speed of the system. Interrupt response time is a very important indicator. Especially in real-time computer systems, interrupt response time is a key indicator of the entire computer system. There are many factors that affect the interrupt service response, such as the priority setting of the interrupt source itself relative to other interrupt sources. Interrupt response is not possible while the core is not suitable or possible to use interrupt technology. Therefore, this time is also equivalent to an interrupt response delay, DMA operation is one of the factors. Because DMA transfers are also equivalent to an interrupt, except that it applies bus control to the processor, not the processor itself. During the DMA transfer, the processor loses control of the bus because it has to give control of the bus to the DMA. Although the processor can do some work without using the bus, it will certainly not respond to external interrupt requests from the bus immediately, thus causing Large interrupt latency. 2 SoC system architecture with DMA 2.1 Introduction to DMA Structure In general, the function and structure of the DMA controller is determined by the system architecture. But as an IP, the DMA controller has its generality. DMA refers to the I/O method in which an external device directly reads and writes to a computer memory. In this way, the reading and writing of data does not require the processor to execute instructions, nor does it go through the internal registers of the processor, but uses the data bus of the system, and the peripherals directly write or read the memory, thereby achieving extremely high transmission efficiency. The importance of DMA technology is that it does not require processor intervention when using it for data access, which increases the efficiency of the system's execution of applications. Another benefit of using DMA to transfer data is that data is transferred directly between the source and destination addresses, without the need for intermediate media. In most AMBA bus-based SoC: systems, when a DMA operation is required, the DMA controller first issues a request to the processor to occupy the bus. When the bus request is successful, the processor hands over the bus usage right to the DMA controller. Data transfer is possible, and the DMA controller releases bus control when the DMA transfer is completed. AMBA is an advanced bus architecture proposed by ARM for on-chip communication of microprocessors. A typical AMBA bus consists of AHB and APB bus segments. The devices on the bus can be divided into a master device (maSTer) capable of active reading and writing and a slave device (slave) capable of receiving only requests from the master. Research on DMA controllers has led to new SoC architectures, such as the use of distributed Fly-by DMA architectures, and the provision of dedicated channels for modules with large data throughput. From the power consumption point of view, when there are more master modules in the system, the burden of the bus arbiter is aggravated, and the arbiter is the main source of AMBA bus power consumption. 2.2 SoC system architecture including AHB master-slave interface DMA controller In order to alleviate the need to realize large-scale data transmission in the same system at the same time, an AMBA bus-based SoC system architecture as shown in FIG. 1 is proposed. As can be seen from the figure, the data interface and instruction interface of the system processor are both attached to the AHB bus as the master of the AHB. The main memory is attached to the AHB bus through the slave interface, and the DMA controller also includes the master and slave interfaces and is attached to the AHB bus. The slave interface is used to configure the internal registers of the DMA controller. The master is used to request the AHB bus control right from the AHB and perform DMA transfer. In Figure 1, Memory is hung on the AHB bus through the AHB slave interface. The DMA controller contains two interfaces. After the slave interface completes the configuration of the DMA internal register, the master interface can apply for the AHB bus usage right. When the license is obtained, the AHB bus is occupied and the DMA data transmission is realized. In this way, the processor is freed from the large-volume data transmission between the peripherals, and is directly completed by the DMA, thereby improving the data transmission rate. But this also has a problem: when the DMA occupies the AHB bus, the processor cannot use the AHB interface to fetch and read and write data. Although most of the processors are equipped with a large cache (Cache) inside or outside the processor, when the DMA controller occupies memory, the processor can continue to run using the programs and data in the Cache; but the Cache is a program Local principle, when the operation performed by the processor has good locality, the instruction and data in the Cache can continue to run during the DMA occupation of the AHB bus, but if there is a device interrupt at this time, the PC pointer of the processor at this time A jump will occur, which will result in a situation where the Cache cannot hit. The AHB bus is occupied by the DMA controller, the processor cannot fetch the finger, and the capacity of the Cache cannot be too large due to the cost problem, thereby affecting the efficiency of the processor. The automotive wiring harness is the network body of the automotive circuit, and there is no automotive circuit without the wiring harness. Wiring harness refers to the contact terminal (connector) made of copper punched and crimped with the wire and cable, and then the outside is pressed with an insulator or an external metal shell, etc., and the wiring harness is bundled to form a component connecting the circuit. automobile wiring harness,vehicle wiring,reliable,durable,electrical Huizhou Fibercan Industrial Co.Ltd , https://www.fibercannetworks.com